-

Resources

Resources

Many of our research papers are published on FPGA conferences and are free for download. Contact us if you want more information.

Event: 2016 26th International Conference on Field Programmable Logic and Applications (FPL)

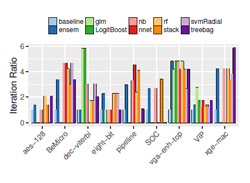

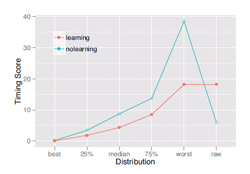

Machine Learning approaches for automated selection of FPGA CAD tool parameters have been demonstrated to be useful for timing closure of FPGA designs [3], [4]. This is achieved by running the CAD tool multiple times with small variations in the the CAD parameter values. The timing slack from each run is recorded into a database along with all input parameter selections to help train a classifier. By progressively running more instances of the tool, we can help drive the CAD tool towards timing convergence…

Improving Classification Accuracy of a Machine Learning approach for FPGA Timing Closure

Improving Classification Accuracy of a Machine Learning approach for FPGA Timing ClosureEvent: 2016 IEEE 24th Annual International Symposium on Field-Programmable Custom Computing Machines (FCCM)

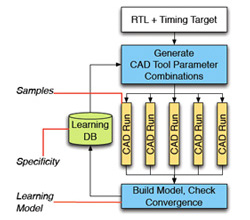

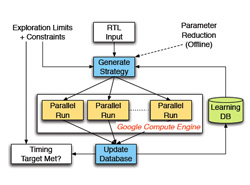

We can use Cloud Computing and Machine Learning to help deliver timing closure of FPGA designs using InTime [2], [3]. This approach requires no modification to the input RTL and relies exclusively on manipulating the CAD tool parameters that drive the optimization heuristics. By running multiple combinations of the parameters in parallel, we learn from results and identify which parameters caused an improvement in the final results…

Case for Design-Specific Machine Learning in Timing Closure of FPGA Designs

Case for Design-Specific Machine Learning in Timing Closure of FPGA DesignsEvent: FPGA ’16 Proceedings of the 2016 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays

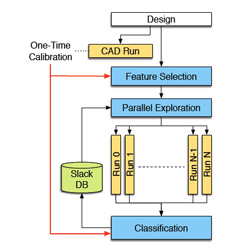

We can achieve reliable timing closure of FPGA designs us ing machine learning heuristics to generate input parameter settings for FPGA CAD tools. This is enabled by running multiple instances of CAD tool with different sets of these input parameters and logging of resulting timing slack values into a database. We incrementally build this database and run learning routines to develop suitable classier models that correlate input parameter combinations to resulting slack. As each CAD run in independent, we can trivially parallelize our exploration…

Driving Timing Convergence of FPGA Designs through Machine Learning and Cloud Computing

Driving Timing Convergence of FPGA Designs through Machine Learning and Cloud ComputingEvent: Field-Programmable Custom Computing Machines (FCCM), 2015 IEEE 23rd Annual International Symposium on 2-6 May 2015

Machine learning and cloud computing techniques can help accelerate timing closure for FPGA designs without any modification to original RTL code. RTL is generally frozen closer to system delivery target to avoid injecting new unforeseen bugs or significantly affecting design characteristics. In these circumstances, developers trying to close timing are either at the mercy of random trials through placement seed exploration…

InTime: A Machine Learning Approach for Efficient Selection of FPGA CAD Tool Parameters

InTime: A Machine Learning Approach for Efficient Selection of FPGA CAD Tool ParametersEvent: FPGA ’15 Proceedings of the 2015 ACM/SIGDA International Symposium on Field-Programmable Gate Arrays

FPGA CAD tool parameters controlling synthesis optimizations, place and route effort, mapping criteria along with user-supplied physical constraints can affect timing results of the circuit by as much as 70% without any change in original source code. A correct selection of these parameters across…