InTime floorplanning is an automated, congestion-aware floorplanning approach. Placement and routing engines of major FPGA tools are well-tuned and robust enough in most cases. However, these engines are often inadequate for designs with high utilization and/or congestion. Floorplanning is necessary to guide these engines to provide better Place & Route results. InTime floorplanning prioritises designs with characteristics such as:

- High utilization designs with congestion on multi-die devices

- Low LUT, High RAM/DSP designs on multi-die devices

- *Single die devices with high routing delays

Automated Floorplanning

Floorplanning in FPGA designs has been predominantly an arduous and manual process. The FPGA tools provide commands and utilities to define, create, position, and manipulate areas of the target devices. The critical decisions regarding the sizes, locations and instances to floorplan, are left to the human designer.

InTime automates these critical decisions and generates multiple effective floorplans.

Floorplanning Modes

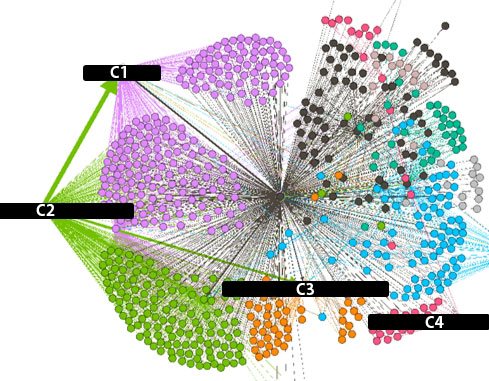

There are 2 automated floorplanning modes available.

Congestion mode

Detects modules responsible for inducing excessive global or localized congestion. InTime floorplans the design to alleviate congestion and prioritises timing critical modules.

Resource Balancing mode

Analyzes hierarchical connectivity across the design to determine the best floorplans that balance connectivity between floorplan partitions, improving overall timing performance.

Assessing Floorplan Results

A fundamental challenge is actually assessing whether the floorplan is overall beneficial or not. Floorplanning is carried out before placement and routing and the results depend on combinations of factors such as locations of I/Os, hard macros and dedicated resources; placement and routing congestion; and many more.

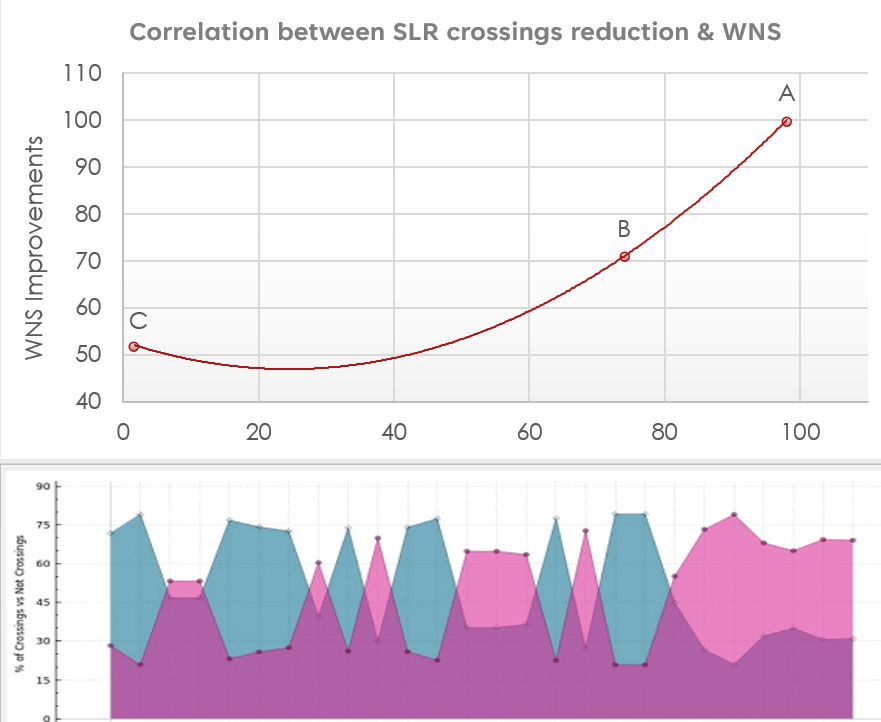

As devices and designs become more complex, these contributing factors complicate the assessment of floorplans. Referring to WNS and TNS is too simplistic in some situations.

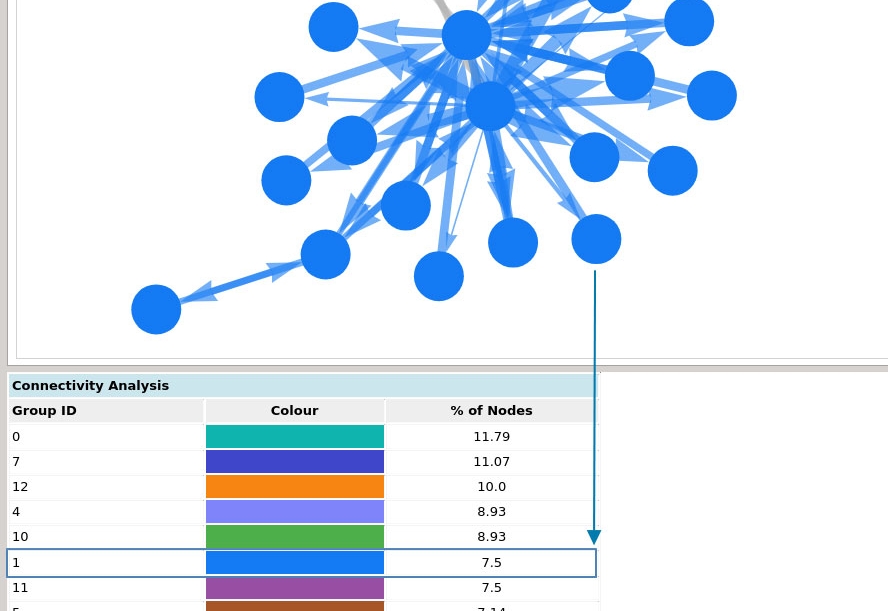

InTime provides specific metrics such as die crossings versus non-crossings for multi-die devices, or the congestion analysis to verify that designs with floorplans have improved.

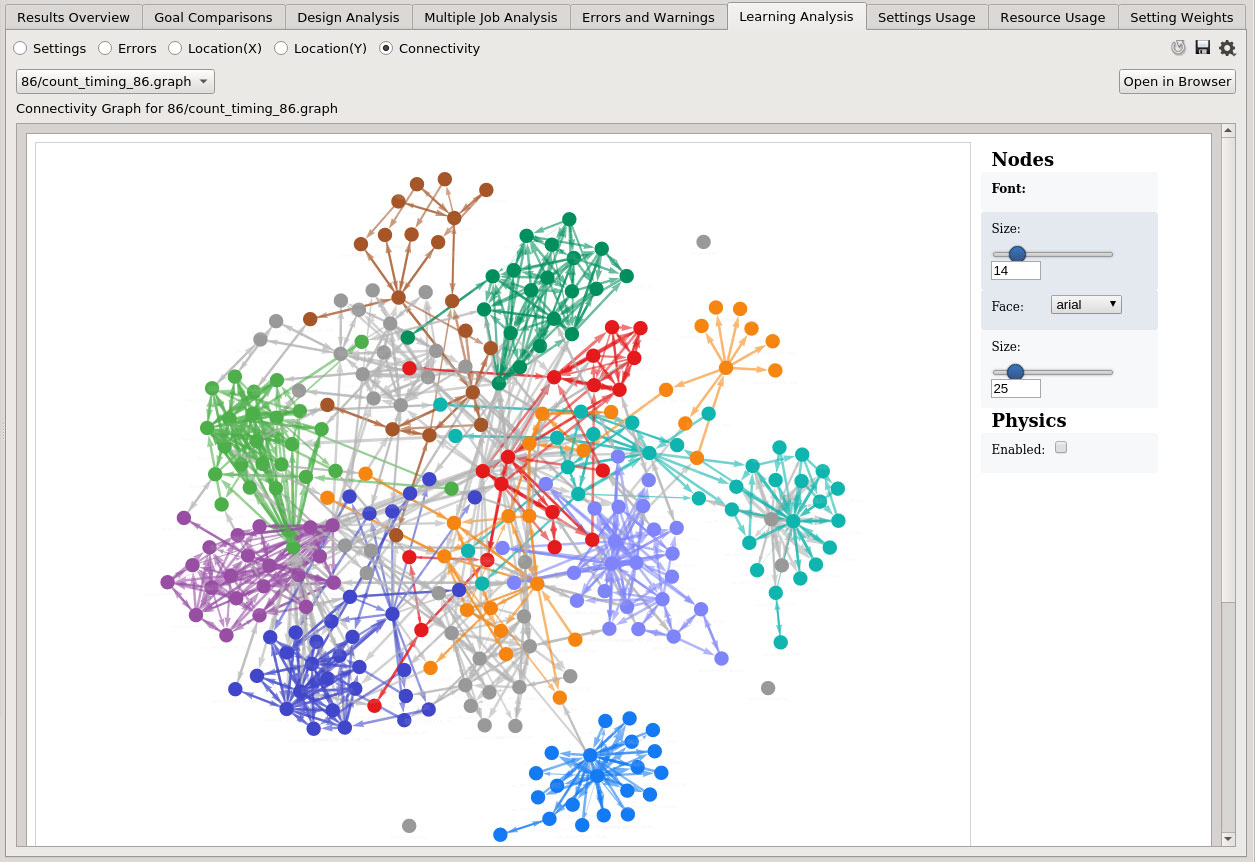

Interactive Connectivity Analysis

InTime connectivity graph can visualize the design’s hierarchy and to understand the connectivity between critical modules. The interactive graph allows users to manipulate the visualization, i.e. drag and/or zoom, to gain insights on relationships between key modules, and to assist and guide manual floorplanning efforts.

Diagnose Design Bottlenecks

Before running the InTime Auto Floorplan Recipe, it is recommended that the user generates a Design Assessment Report. Design Assessment’s primary goal is to make an assessment of the success/failure potential of Placement and Routing of an FPGA design, as well as that of meeting timing. The report contains recommendations on how to mitigate various issues pre-emptively before running InTime Recipes, in order to increase the likelihood of Place & Route and timing closure success.

To learn more about successful floorplanning with InTime, please contact us to find out more.